ČÓ╣”─▄ųŪ─▄DAQįO(sh©©)éõ┼õėąūįČ©┴x╩Į░Õ▌d╠Ä└Ē╣”─▄Ż¼ūŅ┤¾Ž▐Č╚Ąž×ķŽĄĮy(t©»ng)Č©Ģr(sh©¬)╝░ė|░l(f©Ī)╠ß╣®ņ`╗Ņąį─▄ĪŻ ┼c┐žųŲįO(sh©©)éõ╣”─▄Ą─╣╠Č©

ASIC▓╗═¼Ż¼ųŪ─▄DAQ▓╔ė├╗∙ė┌

FPGAĄ─ŽĄĮy(t©»ng)Č©Ģr(sh©¬)┐žųŲŲ„Ż¼┴Ņ╦∙ėą─ŻöM║═öĄ(sh©┤)ūųI/O─▄ē“Ė∙ō■(j©┤)╠žČ©æ¬(y©®ng)ė├▓┘ū„Įė╩▄ŽÓæ¬(y©®ng)Ą─┼õų├ĪŻ ▒ŠųĖ─Žš╣╩Š┴╦Ż║╚ń║╬╩╣ė├RŽĄ┴ąųŪ─▄DAQ░Õ┐©║═NI LabVIEW

FPGAŻ¼ņ`╗Ņūį╚ńĄžł╠(zh©¬)ąąöĄ(sh©┤)ō■(j©┤)▓╔╝»╚╬äš(w©┤)

ĪĪĪĪ╚ļķT

ĪĪĪĪNI LabVIEW FPGA─ŻēKÄ═ų·DAQŽĄĮy(t©»ng)Ą─ķ_░l(f©Ī)š▀ņ`╗Ņūį╚ńĄž▀M(j©¼n)ąąæ¬(y©®ng)ė├│╠ą“ŠÄ│╠ęįīŹ(sh©¬)¼F(xi©żn)Ė„ŅÉ▌ö╚ļ/▌ö│÷▓┘ū„ĪŻ ė├涤oąĶŅA(y©┤)Ž╚┴╦ĮŌVHDLĄ╚ė▓╝■įO(sh©©)ėŗ(j©¼)╣żŠ▀Ż¼▒Ń┐╔īóLabVIEW┤·┤aŪČ╚ļFPGAąŠŲ¼▓ó½@Ą├ė▓╝■Č©Ģr(sh©¬)Ą─╦┘Č╚║═┐╔┐┐ąįĪŻ

ĪĪĪĪūī╬ęéāŽ╚Å─öĄ(sh©┤)ō■(j©┤)▓╔╝»ė▓╝■Ą─│Żė├ĮM╝■Ūą╚ļšōŅ}ĪŻ ╝┘įO(sh©©)─·ōĒėą┴╦─ŻöĄ(sh©┤)▐D(zhu©Żn)ōQŲ„(ADC)ĪóöĄ(sh©┤)─Ż▐D(zhu©Żn)ōQŲ„(DAC)║═öĄ(sh©┤)ūų▌ö╚ļ/▌ö│÷ŠĆŻ¼ät╦∙ėąI/O▒Ńę¬Ė∙ō■(j©┤)īŹ(sh©¬)ļH▓┘ū„Įė╩▄─│ĘNĘĮ╩ĮĄ─Č©Ģr(sh©¬)║═┐žųŲĪŻ Ąõą═Ą─ČÓ╣”─▄öĄ(sh©┤)ō■(j©┤)▓╔╝»įO(sh©©)éõ▓╔ė├╣”─▄²R╚½Ą─ASICŻ¼ØMūŃ┴╦┤¾ČÓöĄ(sh©┤)Ą─╣”─▄ąįąĶŪ¾ĪŻ

ĪĪĪĪ▒╚╚ńŻ║MŽĄ┴ąDAQįO(sh©©)éõ═©▀^DAQ-STC2Ż¼┐žųŲų°Ė„ŅÉė▓╝■ĮM╝■Ą─Č©Ģr(sh©¬)║═ė|░l(f©Ī)ĪŻ ųŪ─▄DAQė▓╝■Ż©╚ńŻ║RŽĄ┴ąDAQįO(sh©©)éõŻ®ģ^(q©▒)äeė┌╩ą├µ╔ŽĄ─Ųõ╦¹╚╬║╬öĄ(sh©┤)ō■(j©┤)▓╔╝»įO(sh©©)éõŻ¼ę“?y©żn)ķį┌┐žųŲįO(sh©©)éõ╣”─▄ĘĮ├µųŪ─▄DAQė├╗∙ė┌FPGAĄ─ŽĄĮy(t©»ng)Č©Ģr(sh©¬)┐žųŲŲ„╚Ī┤·┴╦é„Įy(t©»ng)ASICŻ¼Å─Č°╩╣Ą├╦∙ėą─ŻöM║═öĄ(sh©┤)ūųI/OČ╝─▄Ė∙ō■(j©┤)╠žČ©æ¬(y©®ng)ė├▓┘ū„Įė╩▄ŽÓæ¬(y©®ng)Ą─┼õų├ĪŻ ┐╔ųž┼õų├FPGAąŠŲ¼═©▀^NI LabVIEW FPGA─ŻēK▀M(j©¼n)ąąŠÄ│╠Ż¼┤╦Ģr(sh©¬)NI LabVIEWĄ─öĄ(sh©┤)ō■(j©┤)┴„─Ż╩Į╚į┼f▀mė├Ż¼▓╗▀^▓╔ė├┴╦ę╗ĮMą┬║»öĄ(sh©┤)┐žųŲūŅĄūīėĄ─įO(sh©©)éõI/OĪŻ

ĪĪĪĪLabVIEW FPGA I/O╣Ø(ji©”)³c(di©Żn)▓ó▓╗═©▀^NI-DAQmx║»öĄ(sh©┤)žō(f©┤)ž¤(z©”)īŹ(sh©¬)¼F(xi©żn)│ŻęŖĄ─╚╬äš(w©┤)║═╣”─▄Ż¼Č°╩Ūņ`╗Ņūį╚ńĄžį┌Ė„éĆ(g©©)═©Ą└ūŅĄūīė╔Ž▀\(y©┤n)ąąĪŻ ═©▀^ęįŽ┬Ė„▓┐ĘųĄ─ā╚(n©©i)╚▌Ż¼╬ęéāīó┴╦ĮŌNI-DAQmxĄ─╠žČ©īŹ(sh©¬)└²Ż¼▓óīW(xu©”)┴Ģ(x©¬)╚ń║╬═©▀^ųŪ─▄DAQČ©ųŲĖ„ŅÉöĄ(sh©┤)ō■(j©┤)▓╔╝»╚╬äš(w©┤)ĪŻ

ĪĪĪĪČ©Ģr(sh©¬)║═ė|░l(f©Ī)

ĪĪĪĪīŹ(sh©¬)¼F(xi©żn)Ė▀╝ē(j©¬)öĄ(sh©┤)ō■(j©┤)▓╔╝»Ą─ųŪ─▄DAQų„ę¬ė├ė┌Č©ųŲČ©Ģr(sh©¬)║═ė|░l(f©Ī)ĪŻ Ž┬ĘĮĄ─ĘČ└²│╠ą“┐“łDš╣¼F(xi©żn)┴╦Ż║NI-DAQmxÄ═ų·īŹ(sh©¬)¼F(xi©żn)Ą─ė|░l(f©Ī)╩Į─ŻöM▌ö╚ļ╚╬äš(w©┤)ĪŻ

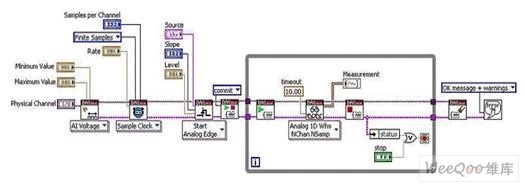

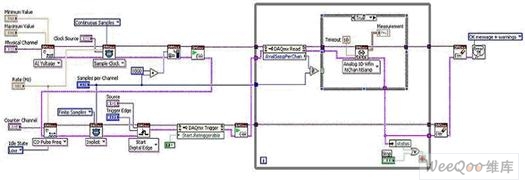

ĪĪĪĪłD1. ═©▀^NI-DAQmxīŹ(sh©¬)¼F(xi©żn)Ą─ė|░l(f©Ī)╩Į─ŻöM▌ö╚ļ

ĪĪĪĪ╚ńłD1╦∙╩ŠŻ¼ųŪ─▄DAQ▓ó╬┤╩╣ė├▓╗═¼║»öĄ(sh©┤)┼õų├═©Ą└Ż¼Č°╩Ū═©▀^├¹×ķI/O╣Ø(ji©”)³c(di©Żn)Ą─║»öĄ(sh©┤)ūxīæĖ„┬Ę─ŻöM║═öĄ(sh©┤)ūų═©Ą└ĪŻ ūī╬ęéā┐┤┐┤╩╣ė├NI LabVIEW FPGAųąI/O╣Ø(ji©”)³c(di©Żn)╦∙½@Ą├Ą─ŽÓ═¼╣”─▄ĪŻ

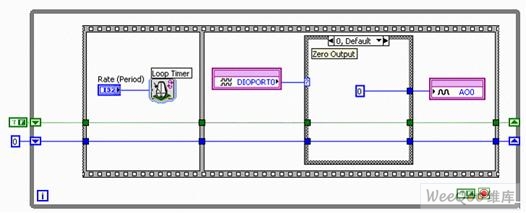

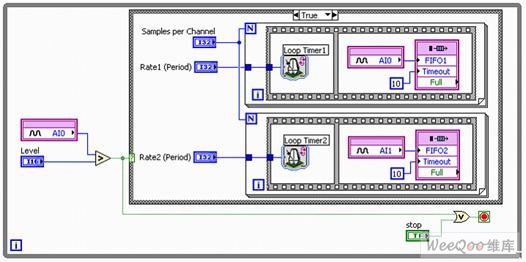

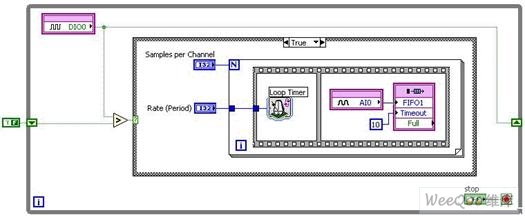

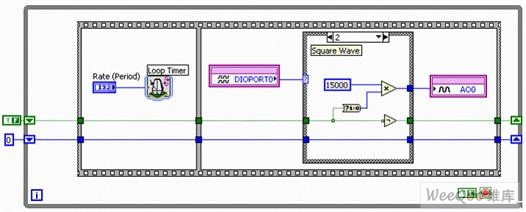

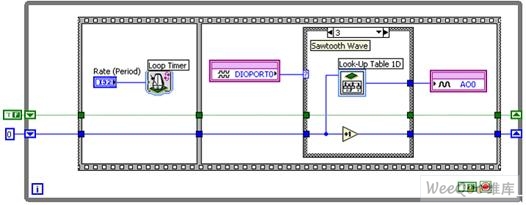

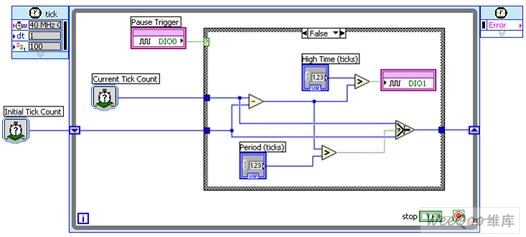

ĪĪĪĪłD2. ═©▀^ųŪ─▄DAQ║═NI LabVIEW FPGAīŹ(sh©¬)¼F(xi©żn)Ą─ė|░l(f©Ī)╩Į─ŻöM▌ö╚ļ

ĪĪĪĪ╔ŽłD╝╚ø]ėąßśī”(du©¼)╚½Šų═©Ą└Īó▓╔śėĢr(sh©¬)ńŖĪóė|░l(f©Ī)Ą─┼õų├║»öĄ(sh©┤)Ż¼ę▓ø]ėąķ_╩╝Īó═Żų╣║═ŪÕ│²Ą╚╚╬äš(w©┤)ĪŻ ╦∙ėąā╚(n©©i)╚▌Č╝▒╗1éĆ(g©©)║å(ji©Żn)å╬Ą──ŻöMI/Oūx╚Ī╦∙╚Ī┤·Ż╗╚½▓┐Č©Ģr(sh©¬)Č╝×ķ▒ŠĄžLabVIEWĮY(ji©”)śŗ(g©░u)Ż©╚ńŻ║While裣h(hu©ón)║═Śl╝■ĮY(ji©”)śŗ(g©░u)Ż®╦∙┐žųŲĪŻė╔ė┌š¹éĆ(g©©)│╠ą“┐“łDŠ∙į┌FPGAė▓╝■ā╚(n©©i)ł╠(zh©¬)ąąŻ¼LabVIEW┤·┤aĄ─▀\(y©┤n)ąą▒Ń¾w¼F(xi©żn)│÷ė▓╝■Č©Ģr(sh©¬)Ą─╦┘Č╚║═┐╔┐┐ąįĪŻ

ĪĪĪĪūī╬ęéāĖ³╔Ņ╚ļĄž┴╦ĮŌę╗Ž┬įō│╠ą“┐“łDĄ─▀\(y©┤n)ąąĘĮ╩ĮĪŻ ─ŻöMI/O╣Ø(ji©”)³c(di©Żn)▓ó▓╗ųĖČ©─│éĆ(g©©)▓╔śė╦┘┬╩Ż¼Č°╩╣ė├For裣h(hu©ón)▓╔╝»Ė„éĆ(g©©)śė▒ŠĪŻ ┼cų«ī”(du©¼)æ¬(y©®ng)Ą─ADCį┌I/O╣Ø(ji©”)³c(di©Żn)▒╗š{(di©żo)ė├Ģr(sh©¬)Ż¼žō(f©┤)ž¤(z©”)ī”(du©¼)▌ö╚ļą┼╠¢(h©żo)▀M(j©¼n)ąąīŹ(sh©¬)ļHöĄ(sh©┤)ūų╗»Ż¼ę“Č°═©▀^For裣h(hu©ón)Įė╩▄Č©Ģr(sh©¬)ĪŻ ╚¶Žļį┌100 kHzĄ─Ņl┬╩Ž┬▀M(j©¼n)ąąą┼╠¢(h©żo)▓╔śėŻ¼ßśī”(du©¼)裣h(hu©ón)Ą─čė▀tŠ═▒žĒÜįO(sh©©)Č©×ķ10 ?sĪŻ 裣h(hu©ón)Ą─Č©Ģr(sh©¬)Ų„║»öĄ(sh©┤)Å─Ą┌2▌å裣h(hu©ón)Ą³┤·ķ_╩╝▒Ń┤_▒Żų°╠žČ©Ą─Ģr(sh©¬)ķgčė▀tŻ¼ė├æ¶ę“Č°─▄ē“═©▀^Ēśą“ĮY(ji©”)śŗ(g©░u)▒ŻūCśė▒Šų«ķg┤µį┌ų°ųĖČ©Ą─Ģr(sh©¬)ķgķgĖ¶ĪŻ NI LabVIEW FPGA*─▄ÅŖ(qi©óng)┤¾Ą─Śl╝■ĮY(ji©”)śŗ(g©░u)Ż¼īŹ(sh©¬)ļH┤·▒Ē┴╦ė├ė┌ĘŌčbĖ„ŅÉ┤·┤aĄ─ė▓╝■ė|░l(f©Ī)ĪŻ ė╔ė┌╦∙ėąĄ─║»öĄ(sh©┤)║═ĮY(ji©”)śŗ(g©░u)Č╝═©▀^▀ē▌ŗå╬į¬į┌ė▓╝■ā╚(n©©i)▀\(y©┤n)ąąŻ¼╦∙ęįŚl╝■ĮY(ji©”)śŗ(g©░u)┤_▒Żķ_╩╝Š▀ėąīŹ(sh©¬)Ģr(sh©¬)10 ?sĢr(sh©¬)ķgŠ½Č╚Ą─▓╔śėĪŻ ūŅ║¾ąĶųĖ│÷Ą─╩ŪŻ¼ė╔ė┌▓┘ū„╬╗ė┌ė▓╝■īėŻ¼ų╗╔µ╝░ÄūéĆ(g©©)īė┤╬Ą─│ķŽ¾╠Ä└ĒŻ¼ę“┤╦ė├涤oąĶŪÕ│²╚╬äš(w©┤)ID╗“ßīĘ┼ā╚(n©©i)┤µĪŻ

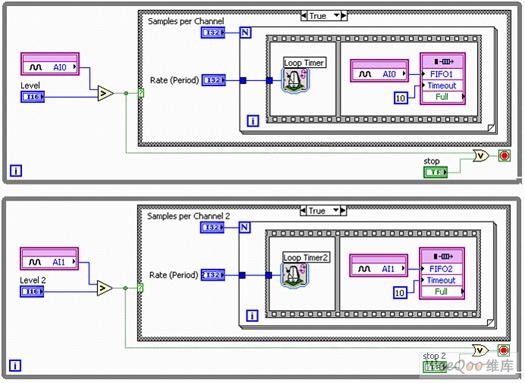

ĪĪĪĪŠ═╗∙ė┌FPGAĄ─ųŪ─▄DAQė▓╝■Č°čįŻ¼Ųõšµš²Ą─ā×(y©Łu)ä▌(sh©¼)╩Ū─▄ē“Č©ųŲĖ„ŅÉČ©Ģr(sh©¬)║═ė|░l(f©Ī)Ż¼▓óį┌ė▓╝■ųą▀M(j©¼n)ąąą┼╠¢(h©żo)╠Ä└Ē║═øQ▓▀ĪŻ ¼F(xi©żn)į┌ūī╬ęéā┴╦ĮŌę╗Ž┬Ż║ßśī”(du©¼)─│ŅÉūįČ©┴xæ¬(y©®ng)ė├Ż¼ąĶī”(du©¼)─ŻöM▌ö╚ļė|░l(f©Ī)ū÷│÷──ą®ą▐Ė─ĪŻ ╚¶╬ęéāŽŻ═¹į┌2┬Ę─ŻöM▌ö╚ļ═©Ą└Ą──│┬ĘļŖē║│¼▀^ųĖČ©ĘČć·Ģr(sh©¬)▒Ńė|░l(f©Ī)▓╔╝»Ż¼ėųįō╚ń║╬ą▐Ė──žŻ┐ ĮĶų·NI LabVIEW FPGAŻ¼┤╦ŅÉ╚╬äš(w©┤)Ą─ł╠(zh©¬)ąąęū╚ńĘ┤šŲĪŻ

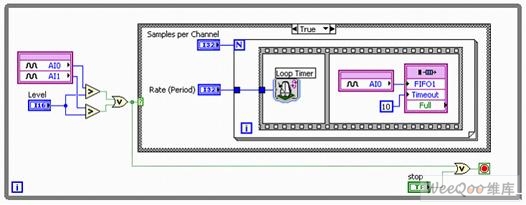

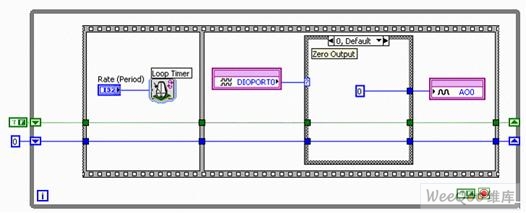

ĪĪĪĪłD 3. ═©▀^ųŪ─▄DAQ║═NI LabVIEW FPGAīŹ(sh©¬)¼F(xi©żn)Ą─ūįČ©┴xė|░l(f©Ī)╩Į─ŻöM▌ö╚ļ

ĪĪĪĪ▀@└’Ż¼╬ęéāęčĮø(j©®ng)×ķ│╠ą“┐“łD╠Ē╝ė┴╦Ą┌2éĆ(g©©)I/O╣Ø(ji©”)³c(di©Żn)║═Ą┌2éĆ(g©©)▒╚▌^║»öĄ(sh©┤)Ż¼ęį╝░1éĆ(g©©)▓╝Ā¢Ī░╗“Ī▒║»öĄ(sh©┤)ĪŻ ųŪ─▄DAQė▓╝■×ķ╦∙ėąĄ──ŻöM▌ö╚ļ═©Ą└╠ß╣®īŻė├ADCŻ¼ę“Č°2┬Ę═©Ą└─▄ē“Įė╩▄═¼▓Į▓╔śėŻ╗═¼Ģr(sh©¬)Ż¼ų╗ę¬╚╬║╬1┬Ę═©Ą└Ą─ļŖē║│¼▀^┴╦ųĖČ©ĘČć·Ż¼Śl╝■ĮY(ji©”)śŗ(g©░u)▒ŃĢ■(hu©¼)ł╠(zh©¬)ąąĪ░šµĪ▒Śl╝■Ż¼▓óķ_╩╝ęį10 ?sĢr(sh©¬)ķgŠ½Č╚▀M(j©¼n)ąą▓╔śėĪŻ šł(q©½ng)ėøūĪŻ║╚▒╔┘ųŪ─▄DAQ▒Ń▓╗┐╔─▄╔·│╔ŅÉ╦ŲĄ─ė|░l(f©Ī)Ż╗į┌Ųõ╦¹DAQė▓╝■╔Žæ¬(y©®ng)ė├Ģr(sh©¬)Ż¼ė|░l(f©Ī)ąĶꬊ▀ėąĖ³Ė▀čė▀tĄ─▄ø╝■Č©Ģr(sh©¬)üĒīŹ(sh©¬)¼F(xi©żn)ĪŻ ╚ń╣¹┤╦║¾╬ęéāŽŻ═¹═©▀^öU(ku©░)š╣īó▒O(ji©Īn)┐žĘČć·Å─2┬Ę═©Ą└čė╔ņų┴╚½▓┐8┬Ę═©Ą└Ż¼╔§ų┴ŽŻ═¹╠Ē╝ėöĄ(sh©┤)ūųė|░l(f©Ī)Ż¼Š═ąĶę¬║å(ji©Żn)╗»ūįČ©┴x┤·┤aĪŻ ╠Ē╝ėŅA(y©┤)ė|░l(f©Ī)Æ▀├Ķ║¾Ż¼ė├æ¶▒Ń┐╔ī”(du©¼)▌ö╚ļ═©Ą└▓╗öÓ▀M(j©¼n)ąą▓╔śė▓óīóöĄ(sh©┤)ō■(j©┤)é„╦═ų┴FIFOŠÅø_Ų„ĪŻ ė|░l(f©Ī)Ų„ę╗Ą®Įė╩▄ūx╚ĪŻ¼F(xi©żn)IFOŠÅø_Ų„║═┤╦║¾Ą─▓╔śė▒Ń┐╔Įø(j©®ng)ė╔DMA═©Ą└Ż¼▒╗é„╦═ų┴ų„ÖC(j©®)ĪŻ

ĪĪĪĪ╚ń╣¹╬ęéāŽŻ═¹ĮĶų·NI-DAQmx“ī(q©▒)äė(d©░ng)Ż¼ī”(du©¼)Ą┌2─ŻöM▌ö╚ļ═©Ą└▀M(j©¼n)ąą▓╔śėŻ¼ätįō│╠ą“┐“łD┼cłD1╦∙╩ŠĄ─ā╚(n©©i)╚▌ŽÓ▓Ņ¤oÄūĪŻ╚╗Č°Ž▐ųŲę└╚╗┤µį┌Ż¼ę“?y©żn)?┬Ę═©Ą└Š∙▒╗Ų╚ę²ė├ŽÓ═¼Ą─ė|░l(f©Ī)Ų„▓óęįŽÓ═¼Ą─Ģr(sh©¬)ńŖŅl┬╩▀M(j©¼n)ąą▓╔śėĪŻ ¼F(xi©żn)į┌╬ęéāüĒ┐┤┐┤Ż║ųŪ─▄DAQ║═NI LabVIEW FPGAÄ═ų·īŹ(sh©¬)¼F(xi©żn)Ą─Ė„ŅÉČÓ═©Ą└▓╔śėĪŻ

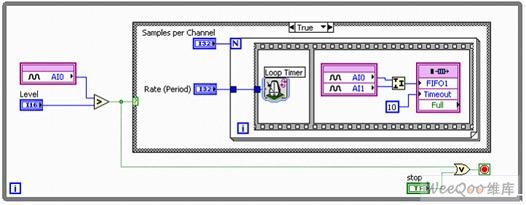

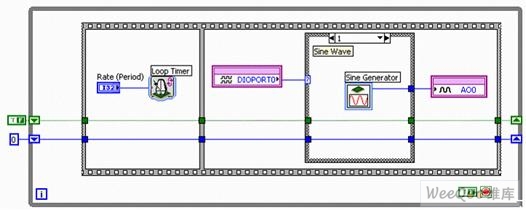

ĪĪĪĪłD4. ═©▀^ųŪ─▄DAQīŹ(sh©¬)¼F(xi©żn)Ą─ė|░l(f©Ī)╩Į═¼▓Į─ŻöM▌ö╚ļ

ĪĪĪĪłD4Ż©╔ŽłDŻ®š╣¼F(xi©żn)┴╦Ż║╚ń║╬╗∙ė┌─ŻöM▌ö╚ļ═©Ą└0ųąĄ──ŻöMė|░l(f©Ī)Ų„Ż¼ī”(du©¼)2┬Ę▓╗═¼Ą──ŻöM▌ö╚ļ═©Ą└▀M(j©¼n)ąą═¼▓Į▓╔śėĪŻė╔ė┌ųŪ─▄DAQįO(sh©©)éõŠ∙┼õėą¬Ü(d©▓)┴óĄ─ADCŻ¼į┌═¼ę╗I/O╣Ø(ji©”)³c(di©Żn)ųąĄ─2┬Ę═©Ą└┐╔į┌═Ļ╚½ŽÓ═¼Ą─Ģr(sh©¬)┐╠Įė╩▄▓╔śėĪŻ Ąõą═Ą─ČÓ╣”─▄DAQįO(sh©©)éõ┐╔═©▀^ę╗éĆ(g©©)ADCČÓ┬ĘÅ═(f©┤)ė├╦∙ėą═©Ą└Ż¼ę“┤╦Ż¼Ė„┬Ę═©Ą└▒žĒÜ╣▓ŽĒŽÓ═¼Ą─▓╔śėĢr(sh©¬)ńŖ║═ė|░l(f©Ī)ŠĆĪŻ łD5Ż©Ž┬łDŻ®š╣¼F(xi©żn)┴╦Ż║ųŪ─▄DAQė▓╝■ŲõīŹ(sh©¬)─▄ē“ęį¬Ü(d©▓)┴óĄ─╦┘┬╩Ż¼ī”(du©¼)▓╗═¼Ą──ŻöM▌ö╚ļ═©Ą└▀M(j©¼n)ąą▓╔śėĪŻ į┌¬Ü(d©▓)┴ó╗ž┬ĘųąĘ┼ų├─ŻöM▌ö╚ļI/O╣Ø(ji©”)³c(di©Żn)║¾Ż¼├┐┬Ę═©Ą└Ģ■(hu©¼)ęį═Ļ╚½▓╗═¼Ą─╦┘┬╩▀M(j©¼n)ąą▓╔śėŻ¼╚╗║¾Ė„ūį═©▀^2ŚlDMA═©Ą└ūxīæė▓▒PĪŻ

ĪĪĪĪłD5. ═©▀^ųŪ─▄DAQīŹ(sh©¬)¼F(xi©żn)Ą─ė|░l(f©Ī)╩ĮČÓ╦┘┬╩─ŻöM▌ö╚ļ

ĪĪĪĪūŅ║¾ąĶųĖ│÷Ą─╩ŪŻ¼╬ęéā?n©©i)¶╩ŪŽŻ═?┬Ę═©Ą└Š▀ėąŽÓ╗ź¬Ü(d©▓)┴óĄ─▓╔śė┬╩║═ķ_╩╝ė|░l(f©Ī)Ż¼ät┐╔ģóšš?q©½ng)D6Ż¼īó╦∙ėąI/O╣Ø(ji©”)³c(di©Żn)Č╝▓┐╩į┌▓óąąčŁŁh(hu©ón)ĮY(ji©”)śŗ(g©░u)ųąĪŻįōĘĮ╩Į│õĘų└¹ė├┴╦FPGAĄ─▓óąąąįŻ¼┤_▒Ż┴╦Ė„ĒŚ(xi©żng)╚╬äš(w©┤)─▄ē“╩╣ė├īŻė├┘Yį┤▓óį┌ł╠(zh©¬)ąąĢr(sh©¬)═Ļ╚½¬Ü(d©▓)┴óė┌Ųõ╦¹▓╔╝»╚╬äš(w©┤)ĪŻ

ĪĪĪĪłD6. ═©▀^ųŪ─▄DAQīŹ(sh©¬)¼F(xi©żn)Ą─¬Ü(d©▓)┴óė|░l(f©Ī)╩ĮČÓ╦┘┬╩─ŻöM▌ö╚ļ

ĪĪĪĪ═¼▓Į

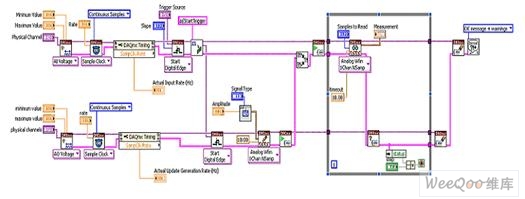

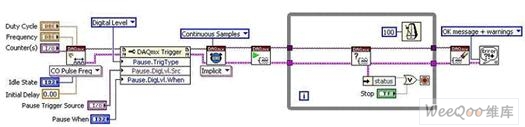

ĪĪĪĪDAQmx“ī(q©▒)äė(d©░ng)│╠ą“╠ß╣®ČÓĘN═¼▓Į▀xō±Ż¼Ä═ų·Į©┴ó▌ö╚ļ║═▌ö│÷Ą─Ģr(sh©¬)ķgŽÓĻP(gu©Īn)ąįĪŻ į┌Ž┬ĘĮĄ─│╠ą“┐“łDųąŻ¼─ŻöM▌ö╚ļ═©Ą└║═─ŻöM▌ö│÷═©Ą└ĮĶų·öĄ(sh©┤)ūųė|░l(f©Ī)īŹ(sh©¬)¼F(xi©żn)═¼▓ĮŻ╗▀^│╠ųąŻ¼ąĶī”(du©¼)─ŻöM▌ö╚ļųĖČ©öĄ(sh©┤)ūųė|░l(f©Ī)Ż¼▓ó╩╣ė├─ŻöM▌ö╚ļĄ─ė|░l(f©Ī)Ų„ą┼╠¢(h©żo)ė|░l(f©Ī)«a(ch©Żn)╔·─ŻöM▌ö│÷ĪŻ

ĪĪĪĪłD7. ═©▀^NI-DAQmxīŹ(sh©¬)¼F(xi©żn)Ą─═¼▓Į─ŻöM▌ö╚ļ║═▌ö│÷

ĪĪĪĪė├æ¶┐╔═©▀^ųŪ─▄DAQė▓╝■▌pČ°ęū┼eĄžł╠(zh©¬)ąą═¼▓Į╚╬äš(w©┤)Ż¼Č°¤oąĶĮĶų·╚╬äš(w©┤)ID║═░Õ▌dą┼╠¢(h©żo)┬Ęė╔ĪŻ ▒Š╠Ä╝┤’@╩Š┴╦NI LabVIEW FPGAųąĄ─ā╚(n©©i)╚▌ĪŻ

ĪĪĪĪłD8. ═©▀^ųŪ─▄DAQīŹ(sh©¬)¼F(xi©żn)Ą─═¼▓Į─ŻöM▌ö╚ļ║═▌ö│÷

ĪĪĪĪ┤╦╠ÄŻ¼╬ęéā?c©©)┘┤╬═©▀^Śl╝■ĮY(ji©”)śŗ(g©░u)į┌FPGAąŠŲ¼╔Žł╠(zh©¬)ąąė▓╝■ė|░l(f©Ī)Ż¼Č°öĄ(sh©┤)ūų═©Ą└0╔ŽĄ─╔Ž╔²čžätåóė├┴╦šµŚl╝■ųąĄ─┤·┤aĪŻ į┌Ēśą“ĮY(ji©”)śŗ(g©░u)ųąŻ¼─ŻöM▌ö╚ļ┼c▌ö│÷Ą─╣Ø(ji©”)³c(di©Żn)į┌═¼Ģr(sh©¬)Įė╩▄š{(di©żo)ė├Ą─▀^│╠ųąŻ¼Äū║§ø]ėą╚╬║╬ČČäė(d©░ng)Ż╗Č°╬ęéāų╗ę¬║å(ji©Żn)å╬Ąžį┌Ė„éĆ(g©©)¬Ü(d©▓)┴óĄ─While裣h(hu©ón)ā╚(n©©i)ŪČ╚ļ─ŻöMI/O╣Ø(ji©”)³c(di©Żn)Ż¼╝┤┐╔┴ŅŲõōĒėą¬Ü(d©▓)┴óĄ─▓╔śė╦┘┬╩ĪŻ ┴Ē═ŌųĄĄ├ūóęŌĄ─╩ŪŻ║ │╠ą“┐“łDųą’@╩ŠĄ─š²Žę░l(f©Ī)╔·Ų„║»öĄ(sh©┤)╩Ū1éĆ(g©©)Express VIŻ¼┐╔Ä═ų·ė├æ¶į┌▓ķšę▒Ē(LUT)ųąĮ╗╗ź╩ĮĄž┼õų├š²ŽęųĄĪŻ

ĪĪĪĪłD8ųąĄ─ųŪ─▄DAQ│╠ą“┐“łD┼cłD7ųąĄ─DAQmx VIĮįŠ▀ėąŽÓ═¼Ą─╣”─▄Ż¼Č°╬©ėąųŪ─▄DAQ▓┼─▄×ķūįČ©┴x╚╬äš(w©┤)╠ß╣®ŽÓæ¬(y©®ng)Ą─ņ`╗ŅąįĪŻ ┼e└²×ķūCŻ║╚ńąĶ╠Ē╝ė1éĆ(g©©)Ģ║═Żė|░l(f©Ī)Ż¼╬ęéāų╗Ž¹į┌ā╚(n©©i)▓┐While裣h(hu©ón)ųą╠Ē╝ė1éĆ(g©©)Śl╝■ĮY(ji©”)śŗ(g©░u)Ż¼▓ó═©▀^┴Ēę╗éĆ(g©©)öĄ(sh©┤)ūųI/O╣Ø(ji©”)³c(di©Żn)▀xō±šµŚl╝■╗“╝┘Śl╝■Ż¼╝┤┐╔▌p╦╔═Ļ│╔╚╬äš(w©┤)ĪŻ ī”(du©¼)ė▓╝■▀M(j©¼n)ąąŠÄ│╠Ą─ÅŖ(qi©óng)┤¾╣”─▄Ż¼īŹ(sh©¬)¼F(xi©żn)┴╦Ė„ŅÉI/OĄ─Č©Ģr(sh©¬)┼c═¼▓ĮĪŻ

ĪĪĪĪČÓ╣”─▄═¼▓ĮĄ─┴Ēę╗└²ūC¾w¼F(xi©żn)×ķŻ║═©▀^░Õ▌dėŗ(j©¼)öĄ(sh©┤)Ų„«a(ch©Żn)╔·ėąŽ▐├}ø_▓óīóėŗ(j©¼)öĄ(sh©┤)Ų„▌ö│÷ė├ū„─ŻöM▌ö╚ļĄ─▓╔śėĢr(sh©¬)ńŖĪŻ įō▀^│╠╩Ū▀M(j©¼n)ąą┐╔ųžė|░l(f©Ī)╩ĮėąŽ▐▓╔śėĄ─│Żė├╩ųČ╬ĪŻ Ž┬łD’@╩Š┴╦ķ_š╣┤╦ŅÉ▓╔╝»╦∙▒žąĶĄ─DAQmx┤·┤aĪŻ

ĪĪĪĪłD9. ═©▀^NI-DAQmxīŹ(sh©¬)¼F(xi©żn)Ą─┐╔ųžė|░l(f©Ī)╩ĮėąŽ▐─ŻöM▌ö╚ļ

ĪĪĪĪ¼F(xi©żn)į┌Ż¼ūī╬ęéāī”(du©¼)Ž┬łDā╚(n©©i)╚▌║═│╩¼F(xi©żn)ŽÓ═¼╣”─▄Ą─NI LabVIEW FPGA│╠ą“┐“łDŻ¼╝ėęį▒╚▌^ĪŻ

ĪĪĪĪłD10. ═©▀^ųŪ─▄DAQ║═NI LabVIEW FPGAīŹ(sh©¬)¼F(xi©żn)Ą─┐╔ųžė|░l(f©Ī)╩ĮėąŽ▐─ŻöM▌ö╚ļ

ĪĪĪĪė╔ė┌NI LabVIEW┤·┤aį┌ė▓╝■īė▀\(y©┤n)ąąŻ¼łD10ųąĄ─“ī(q©▒)äė(d©░ng)┼õų├▓Į¾E’@╚╗Ą├ĄĮ┴╦śO┤¾Š½£pĪŻ ╬ęéāęčĮø(j©®ng)ĮĶų·║å(ji©Żn)å╬Ą─öĄ(sh©┤)ūų▌ö╚ļŠĆ║═For裣h(hu©ón)ĮY(ji©”)śŗ(g©░u)Ż¼äō(chu©żng)Į©┴╦ė▓╝■┐╔ųžė|░l(f©Ī)╩ĮėąŽ▐▓╔╝»ĪŻ łD9ųąĄ─│╠ą“┐“łD╩╣ė├2éĆ(g©©)░Õ▌dėŗ(j©¼)öĄ(sh©┤)Ų„Ż¼äō(chu©żng)Į©│÷┐╔ųžė|░l(f©Ī)Ą─ėąŽ▐├}ø_ą“┴ąŻ╗Ąõą═Ą─ČÓ╣”─▄DAQįO(sh©©)éõų╗ėą2éĆ(g©©)ėŗ(j©¼)öĄ(sh©┤)Ų„ĪŻ Č°ĮĶų·NI LabVIEW FPGAŻ¼ųŪ─▄DAQė▓╝■ģs─▄ē“?q©▒)ó╚╬ęŌę╗ŚlöĄ(sh©┤)ūųŠĆ┼õų├│╔ėŗ(j©¼)öĄ(sh©┤)Ų„ĪŻ ╬ęéāīóį┌ų«║¾Ą─Č╬┬õ└’Ż¼╔µ╝░Ė³ČÓĪ░═©▀^ųŪ─▄DAQ▀\(y©┤n)ąąėŗ(j©¼)öĄ(sh©┤)Ų„/Č©Ģr(sh©¬)Ų„Ī▒Ą─ā╚(n©©i)╚▌ĪŻ

ĪĪĪĪ╬ęéā─▄ē“ĮĶų·ė╔Ņl┬╩ė|░l(f©Ī)Ą─▓╔╝»Ż¼▀M(j©¼n)ę╗▓ĮĄž═Ų▀M(j©¼n)ųŪ─▄DAQį┌ė▓╝■Č©Ģr(sh©¬)ĘĮ├µĄ─ņ`╗Ņąį╠žąįĪŻ ė├æ¶┐╔═©▀^Ė▀╦┘░Õ▌døQ▓▀ėŗ(j©¼)╦Ń▌ö╚ļą┼╠¢(h©żo)Ą─Ņl┬╩Ż¼Č°║¾▀xō±Śl╝■ĮY(ji©”)śŗ(g©░u)ųą╦∙ąĶĄ─┤·┤aŻ╗▀@ę╗³c(di©Żn)╩Ū╩╣ė├Ąõą═ČÓ╣”─▄DAQįO(sh©©)éõ╦∙¤oĘ©Ų¾╝░Ą─ĪŻ į┌ČÓįO(sh©©)éõĄ─═¼▓Į▀M(j©¼n)│╠ųąŻ¼ųŪ─▄DAQ▀Ć┐╔╠ß╣®ė├ė┌PCI░Õ┐©Ą─RTSI┐éŠĆ╗“╩Ūė├ė┌PXI─ŻēKĄ─PXIė|░l(f©Ī)┐éŠĆĪŻ ▀@ą®═Ō▓┐Č©Ģr(sh©¬)║══¼▓ĮŠĆ▀Ć┐╔═©▀^│╠ą“┐“łD╔ŽĄ─I/O╣Ø(ji©”)³c(di©Żn)Įė╩▄įLå¢ĪŻ

ĪĪĪĪ─ŻöM▓©ą╬Ą─╔·│╔

ĪĪĪĪ▓╗╔┘ČÓ╣”─▄DAQįO(sh©©)éõČ╝┼õėą─ŻöM▌ö│÷═©Ą└Ż¼─▄ē“?y©żn)ķ┴╦╔·│╔▀B└m(x©┤)Ą──ŻöM▓©ą╬Č°ąĶę¬ė├ĄĮFIFOŠÅø_ĪŻ ╔·│╔Ą─▓©ą╬┐╔īóFIFOė├ū„裣h(hu©ón)ŠÅø_ģ^(q©▒)Ż¼Ūę¤oąĶÅ─ų„ÖC(j©®)╠ÄĮė╩▄╚╬║╬Ė³ą┬öĄ(sh©┤)ō■(j©┤)Ż¼╝┤┐╔▀B└m(x©┤)▓╗öÓĄžųžą┬╔·│╔ę╗ŽĄ┴ąĄ──ŻöMųĄĪŻ ═©ą┼┐éŠĆĄ─ėą¤oī”(du©¼)┤╦ė░Ēæ▓╗┤¾Ż¼ę“?y©żn)ķ▓óø]ėąßśī”(du©¼)įO(sh©©)éõĄ─ŅlĘ▒öĄ(sh©┤)ō■(j©┤)ūxīæĪŻ Č°╚ń╣¹▓©ą╬ąĶꬹ▐Ė─Ż¼Š═▒žĒÜųžą┬åóäė(d©░ng)▌ö│÷╚╬äš(w©┤)▓óŽ“FIFOīæ╚ļą┬öĄ(sh©┤)ō■(j©┤)ĪŻ ┴Ēę╗éĆ(g©©)▐kĘ©╩ŪŽ“ė▓╝■FIFOįO(sh©©)éõ▀B└m(x©┤)ūxīæöĄ(sh©┤)ō■(j©┤)Ż¼Č°▀@ėųĢ■(hu©¼)ī¦(d©Żo)ų┬▌ö│÷╚╬äš(w©┤)│÷¼F(xi©żn)Ģr(sh©¬)£■ĪŻ ĮĶų·ųŪ─▄DAQŻ¼ė├æ¶─▄ē“?q©▒)ó▓©ą╬▌ö│÷ĮY(ji©”)╣¹┤µā”(ch©│)ė┌ė▓╝■Ż¼╔§ų┴─▄ē“═©▀^ė▓╝■ė|░l(f©Ī)Ė─ūā▓©ą╬Ż¼▀M(j©¼n)Č°äō(chu©żng)Į©╚╬ęŌ▓©ą╬░l(f©Ī)╔·Ų„ĪŻ

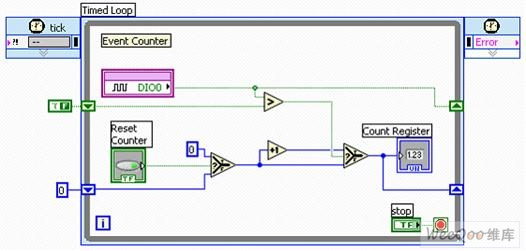

ĪĪĪĪŽ┬ĘĮĄ─║»öĄ(sh©┤)░l(f©Ī)╔·Ų„ĘČ└²═©▀^öĄ(sh©┤)ūų▌ö╚ļŠĆŻ¼ė|░l(f©Ī)┴╦▌ö│÷▓©ą╬ųąĄ─Ė─äė(d©░ng)ĪŻ ═©▀^ĮM║ŽöĄ(sh©┤)ūųI/OŠĆ0┼c1Ż¼╬ęéā?n©©i)ĪĄ├┴╦æ?y©®ng)ė├ė┌─ŻöM▌ö│÷Ą─4ĘN▓╗═¼ĀŅæB(t©żi)╗“ĘQŚl╝■ĪŻ

ĪĪĪĪłD11a. ┼õėąųŪ─▄DAQŚl╝■0Ą─║»öĄ(sh©┤)░l(f©Ī)╔·Ų„ ©C ┴Ń▌ö│÷

ĪĪĪĪłD11b. ┼õėąųŪ─▄DAQŚl╝■1Ą─║»öĄ(sh©┤)░l(f©Ī)╔·Ų„ ©C š²Žę▓©

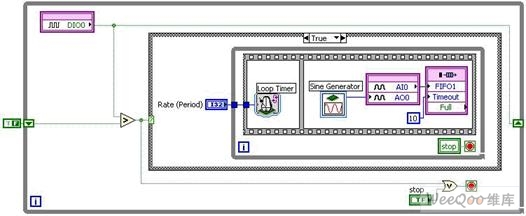

ĪĪĪĪ«ö(d©Īng)ā╔ŠĆĮį│╩¼F(xi©żn)Ą═ļŖŲĮĢr(sh©¬)Ż¼ł╠(zh©¬)ąąŚl╝■0Ż╗╚ńłD11a╦∙╩ŠŻ¼▌ö│÷ųĄ×ķ0 V│Ż┴┐ĪŻČ°«ö(d©Īng)DIOŠĆ0│╩¼F(xi©żn)Ė▀ļŖŲĮČ°DIOŠĆ1│╩¼F(xi©żn)Ą═ļŖŲĮĢr(sh©¬)Ż¼Śl╝■1īóį┌─ŻöM▌ö│÷0╔Žł╠(zh©¬)ąą▓ó╔·│╔ę╗éĆ(g©©)š²Žę▓©ĪŻė├æ¶┐╔═©▀^įōš²Žę╔·│╔ĮY(ji©”)śŗ(g©░u)Ż©łD11bŻ®ųąĄ─š²Žę░l(f©Ī)╔·Ų„Express VIŻ¼┼õų├NI LabVIEW FPGA▒žąĶĄ─ģóöĄ(sh©┤)Ż¼Į╗╗źĄž┼õų├š²Žę▓©ĪŻ

ĪĪĪĪłD11c. ┼õėąųŪ─▄DAQŚl╝■2Ą─║»öĄ(sh©┤)░l(f©Ī)╔·Ų„ ©C ĘĮ▓©

ĪĪĪĪŚl╝■2Ż©łD11cŻ®─▄ē“į┌While裣h(hu©ón)Ą─├┐▌åĄ³┤·ųąŻ¼▌p╦╔ŪąōQ▓╝Ā¢ųĄĪŻ öĄ(sh©┤)ųĄ▌^Ą═Ģr(sh©¬)Ż¼š¹öĄ(sh©┤)15000▒Ń▒╗īæ╚ļ─ŻöM▌ö│÷AO0Ż¼ęįī”(du©¼)æ¬(y©®ng)16╬╗DACā╚(n©©i)ė╔▌ö│÷╝─┤µŲ„┤µĘ┼Ą─öĄ(sh©┤)ųĄŻ║15000ĪŻ 16╬╗ėąĘ¹╠¢(h©żo)š¹öĄ(sh©┤)┐╔ęį░³║¼-32768ĄĮ32767ų«ķgĄ─öĄ(sh©┤)ųĄĪŻ«ö(d©Īng)▌ö│÷ļŖē║ĘČć·Įķė┌-10 V║═10 VĢr(sh©¬)Ż¼Ž“─ŻöM▌ö│÷AO0īæ╚ļ-32768Ģ■(hu©¼)╔·│╔-10 VļŖē║Ż¼Č°īæ╚ļ32767ät╔·│╔10 VļŖē║ĪŻįō└²ųąŻ¼ę“╬ęéāĄ─īæ╚ļųĄ×ķ15000Ż¼ät╔·│╔Ą─ļŖē║īóĄ═ė┌5 VĪŻŻ©öĄ(sh©┤)īW(xu©”)╣½╩Į×ķ: 15000/32767 * 10 V = 4.5778 VŻ® ═©│ŻŻ¼Śl╝■2Ģ■(hu©¼)▌ö│÷ę╗éĆ(g©©)į┌0 V║═4.578 Vų«ķgūāōQĄ─ĘĮ▓©ĪŻ

ĪĪĪĪłD11d. ┼õėąųŪ─▄DAQŚl╝■3Ą─║»öĄ(sh©┤)░l(f©Ī)╔·Ų„ ©C õŲX▓©

ĪĪĪĪ«ö(d©Īng)DIO 0║═DIO 1Š∙│╩¼F(xi©żn)Ė▀ļŖŲĮĢr(sh©¬)Ż¼▒Ńł╠(zh©¬)ąąūŅ║¾ę╗éĆ(g©©)Śl╝■Ż©łD11dŻ®Ż╗ŲõķgŻ¼ĒÜĮĶų·▓ķšę▒Ē(LUT)▀B└m(x©┤)╔·│╔ę╗éĆ(g©©)õŲX▓©ĪŻ ū„×ķ┴Ēę╗ŅÉExpress VIĄ─▓ķ▒ĒVIŻ¼╝╚─▄┤µā”(ch©│)╚╬ęŌ▓©ą╬ųĄŻ¼ę▓─▄═©▀^ŠÄ│╠Į©┴ó▓©ą╬ųĄĄ─╦„ę²ĪŻ įō└²ųąŻ¼Įė╩▄┼õų├Ą─õŲX▓©┐╔į┌─ŻöM▌ö│÷═©Ą└0╔Ž╔·│╔ĪŻ

ĪĪĪĪ═©▀^īó╦∙ėąĄ─ųĄČ╝┤µā”(ch©│)į┌FPGA╔ŽŻ¼ė├æ¶į┌ĮĄĄ═┐éŠĆę└┘ćąįĄ─═¼Ģr(sh©¬)Ż¼ę▓┤_▒Ż┴╦▓©ą╬Ė³ą┬Ģr(sh©¬)ė▓╝■Č©Ģr(sh©¬)Ą─╦┘Č╚║═┐╔┐┐ąįĪŻ ų«Ū░Ė„▓┐Ęųųą╦∙├Ķ╩÷Ą──ŻöM▌ö╚ļĄ─ė|░l(f©Ī)║══¼▓Įņ`╗Ņąį═¼śė▀mė├ė┌─ŻöM▌ö│÷Ż╗ĮĶų·ųŪ─▄DAQŻ¼ė├æ¶─▄ē“ęį▓╗═¼╦┘┬╩Ż¼═Ļ╚½¬Ü(d©▓)┴óĄžĖ³ą┬Ė„┬Ę─ŻöM▌ö│÷═©Ą└ĪŻ ▀@ęŌ╬Čų°Ż║ė├æ¶┐╔į┌▓╗ė░ĒæŲõ╦¹═©Ą└▌ö│÷ĮY(ji©”)╣¹Ą─Ū░╠ߎ┬Ż¼ą▐Ė─å╬éĆ(g©©)ų▄Ų┌ąį▓©ą╬Ą─Ņl┬╩ĪŻ šł(q©½ng)ūóęŌŻ║┤¾ČÓöĄ(sh©┤)öĄ(sh©┤)ō■(j©┤)▓╔╝»ė▓╝■Š∙▓╗Š▀éõ┤╦ĒŚ(xi©żng)╣”─▄ĪŻ

ĪĪĪĪėŗ(j©¼)öĄ(sh©┤)Ų„/Č©Ģr(sh©¬)Ų„Ą─▓┘ū„

ĪĪĪĪ╚ńŪ░╦∙╩÷Ż¼Ąõą═Ą─ČÓ╣”─▄DAQįO(sh©©)éõų╗ėą2éĆ(g©©)░Õ▌dėŗ(j©¼)öĄ(sh©┤)Ų„Ż¼Č°ųŪ─▄DAQät─▄į┌Ė„ŚlöĄ(sh©┤)ūųŠĆ╔Ž▀\(y©┤n)ąąėŗ(j©¼)öĄ(sh©┤)Ų„╣”─▄ĪŻ öĄ(sh©┤)ūųI/O╣Ø(ji©”)³c(di©Żn)─▄ē“į┌NI LabVIEW FPGAųą└¹ė├├¹×ķå╬ų▄Ų┌Č©Ģr(sh©¬)裣h(hu©ón)Ą─īŻśI(y©©)ĮY(ji©”)śŗ(g©░u)Ż¼Ä═ų·ė├æ¶į┌2.5 MHzų┴200 MHzĄ─╠žČ©Ņl┬╩ĘČć·ā╚(n©©i)ł╠(zh©¬)ąą┤·┤aĪŻ └²╚ńŻ¼ĮĶų·40 MHzĄ─Ģr(sh©¬)ńŖŻ¼ė├æ¶┐╔╩╣ė├å╬ų▄Ų┌Č©Ģr(sh©¬)裣h(hu©ón)Ż¼į┌Ė„ŚlöĄ(sh©┤)ūųŠĆ╔Žäō(chu©żng)Į©40 MHzėŗ(j©¼)öĄ(sh©┤)Ų„ĪŻ łD12Ż©Ž┬łDŻ®š╣¼F(xi©żn)┴╦│╠ą“┐“łDĄ─śė╩ĮĪŻ

ĪĪĪĪłD12. ┼õėąųŪ─▄DAQĄ─║å(ji©Żn)å╬╩┬╝■ėŗ(j©¼)öĄ(sh©┤)Ų„

ĪĪĪĪė╔ė┌ėŗ(j©¼)╦ŃųĄ╗∙ė┌U32Ż©32╬╗š¹öĄ(sh©┤)Ż®Ą─öĄ(sh©┤)ō■(j©┤)ŅÉą═▒╗░l(f©Ī)╦═ų┴’@╩Š┐ž╝■Ż¼įō┤·┤a▒Ńį┌FPGAąŠŲ¼╔Ž╔·│╔┴╦1éĆ(g©©)40 MHzĄ─32╬╗ėŗ(j©¼)öĄ(sh©┤)Ų„ĪŻ ė├æ¶┐╔ī”(du©¼)Ųõ▀M(j©¼n)ąąöĄ(sh©┤)┤╬Å═(f©┤)ųŲ┼cš│┘NŻ¼┴Ņ▓╗═¼öĄ(sh©┤)ūųŠĆ╔ŽĄ─ČÓéĆ(g©©)ėŗ(j©¼)öĄ(sh©┤)Ų„Č╝─▄ē“▒╦┤╦═Ļ╚½▓󹹥ž▀\(y©┤n)ąąĪŻ ═©▀^ī”(du©¼)ųŪ─▄DAQųąģóöĄ(sh©┤)Ą─įO(sh©©)ų├┐╔ęįīŹ(sh©¬)¼F(xi©żn)Č©Ģr(sh©¬)Ų„▓┘ū„Ą─ūįČ©┴xĪŻ ═©▀^▀xō±Ż¼ė├æ¶─▄ē“├┐Ė¶2éĆ(g©©)╔Ž╔²čž▒Ń▀M(j©¼n)ąą1┤╬ėŗ(j©¼)öĄ(sh©┤)Ų„▀fį÷Ż¼╔§ų┴─▄╗∙ė┌ėŗ(j©¼)öĄ(sh©┤)╝─┤µŲ„Ą─ųĄė|░l(f©Ī)─ŻöM▓╔╝»ĪŻ įSČÓÅ═(f©┤)ļsĄ─ėŗ(j©¼)öĄ(sh©┤)Ų„▓┘ū„Ż©╚ńŻ║ėąŽ▐├}ø_ą“┴ą╔·│╔║═╝ē(j©¬)┬ō(li©ón)╩Į╩┬╝■ėŗ(j©¼)öĄ(sh©┤)Ż®Š∙ąĶę¬╩╣ė├2éĆ(g©©)ėŗ(j©¼)öĄ(sh©┤)Ų„Ż¼▀@ęŌ╬Čų°╩╣ė├Ąõą═ČÓ╣”─▄įO(sh©©)éõųąĄ─╦∙ėą░Õ▌dėŗ(j©¼)öĄ(sh©┤)Ų„ĪŻ į┌┐é╣▓160ŚlöĄ(sh©┤)ūųŠĆĄ─Ä═ų·Ž┬Ż¼ųŪ─▄DAQė▓╝■╔ŽČ©Ģr(sh©¬)Ų„Ą─ūŅ┤¾öĄ(sh©┤)┴┐║▄╔┘╩▄ĄĮI/O┐╔ė├ąįĄ─ė░ĒæŻ¼Č°═∙═∙╚ĪøQė┌FPGAąŠŲ¼Ą─┤¾ąĪĪŻ ė╔ė┌NI LabVIEW┤·┤a▀\(y©┤n)ąąė┌╣ĶąŠŲ¼ųąŻ¼ę“Č°ė├涤oąĶĪ░čbéõĪ▒╗“Ī░ųžą┬čbéõĪ▒═©ė├ėŗ(j©¼)öĄ(sh©┤)Ų„Ż¼╝┤─▄╚½├µ┐žųŲėŗ(j©¼)öĄ(sh©┤)Ų„Ą─▀\(y©┤n)ąąĪŻ

ĪĪĪĪłD13Ż©Ž┬łDŻ®ųąĄ─ĘČ└²╩╣ė├ėŗ(j©¼)öĄ(sh©┤)Ų„Ż¼╔·│╔┴╦ę╗éĆ(g©©)▀B└m(x©┤)├}ø_ą“┴ą▓óīóĢ║═Żė|░l(f©Ī)Ų„ų├ė┌NI-DAQmxųąĪŻ

ĪĪĪĪłD13. ▀B└m(x©┤)├}ø_ą“┴ąĄ─╔·│╔║═┼õėąNI-DAQmxĄ─Ģ║═Żė|░l(f©Ī)Ų„

ĪĪĪĪį┌NI LabVIEW FPGAųąŻ¼Ģ║═Żė|░l(f©Ī)Ų„¤oąĶĮė╩▄┼õų├Ż¼ę“?y©żn)ķų╗ąĶ║?ji©Żn)å╬Ą─Śl╝■ĮY(ji©”)śŗ(g©░u)▒Ń─▄į┌╣ĶąŠŲ¼ųąīŹ(sh©¬)¼F(xi©żn)ŽÓ═¼Ą─╣”─▄ĪŻ ┤╦╠Ä╩Ū═©▀^ųŪ─▄DAQ▀\(y©┤n)ąąĢr(sh©¬)╦∙š╣¼F(xi©żn)Ą─ŽÓ═¼╣”─▄Ż©łD14Ż®ĪŻ

ĪĪĪĪłD14. ▀B└m(x©┤)├}ø_ą“┴ąĄ─╔·│╔║═┼õėąųŪ─▄DAQĄ─Ģ║═Żė|░l(f©Ī)Ų„

ĪĪĪĪį┌▀@ĘNŪķørŽ┬Ż¼öĄ(sh©┤)ūųI/OŠĆDIO0ė├ū„Ģ║═Żė|░l(f©Ī)Ż¼Č°├}ø_īóį┌öĄ(sh©┤)ūųI/OŠĆDIO1╔Ž╔·│╔▓ó▌ö│÷ĪŻ╩╣ė├å╬ų▄Ų┌Č©Ģr(sh©¬)裣h(hu©ón)┐╔┴ŅĖ„éĆ(g©©)├}ø_½@Ą├25 nsĄ─Ęų▒µ┬╩Ż¼ę“?y©żn)ķ▀@īó│╔×ķå╬éĆ(g©©)ėŗ(j©¼)Ģr(sh©¬)į┌╩╣ė├40 MHzČ©Ģr(sh©¬)į┤Ģr(sh©¬)Ą─ųĄĪŻ

ĪĪĪĪöĄ(sh©┤)ūųI/Oæ¬(y©®ng)ė├

ĪĪĪĪųŪ─▄DAQė▓╝■╠ß╣®ČÓ▀_(d©ó)160Ślė▓╝■Č©Ģr(sh©¬)öĄ(sh©┤)ūųŠĆŻ¼┴ŅųTČÓöĄ(sh©┤)ūųæ¬(y©®ng)ė├│╔×ķ┐╔─▄ĪŻ ╬ęéāęčĮø(j©®ng)īW(xu©”)┴Ģ(x©¬)┴╦╚ń║╬╩╣ė├öĄ(sh©┤)ūųI/OīŹ(sh©¬)¼F(xi©żn)ė|░l(f©Ī)Īó═¼▓Į╝░ėŗ(j©¼)öĄ(sh©┤)Ų„/Č©Ģr(sh©¬)Ų„Ą─▀\(y©┤n)ąąŻ¼Č°ųŪ─▄DAQ▀Ć┐╔ė├ė┌š`┤a┬╩£y(c©©)įćĪóöĄ(sh©┤)ūų─Ż╩ĮŲź┼õĪó├}ø_īÆČ╚š{(di©żo)ųŲĪóš²Į╗ŠÄ┤aŲ„║═öĄ(sh©┤)ūų═©ą┼ģf(xi©”)ūhĪŻ ūįČ©┴x╗“ś╦(bi©Īo)£╩(zh©│n)ą╬╩ĮĄ─┤«ąąĮė┐┌Š∙─▄ų▒Įė═©▀^öĄ(sh©┤)ūųČ©Ģr(sh©¬)┐“łDŠÄ│╠üĒīŹ(sh©¬)¼F(xi©żn)ĪŻ ┼e└²šf├„Ż¼SPI▒Ń╩Ūę╗┐Ņ┼cė▓╝■ĮM╝■Ż©╚ńŻ║╬ó┐žųŲŲ„╗“ADCŻ®▀M(j©¼n)ąą═©ą┼Ģr(sh©¬)ūŅ│Żė├Ą─┤«┐┌ģf(xi©”)ūhĪŻ łD15Ż©Ž┬łDŻ®š╣¼F(xi©żn)┴╦į┌▀M(j©¼n)ąą16╬╗SPI═©ą┼Ģr(sh©¬)Ż¼3Śl▒žę¬öĄ(sh©┤)ūųŠĆ╦∙ī”(du©¼)æ¬(y©®ng)Ą─Č©Ģr(sh©¬)┐“łDĪŻ

ĪĪĪĪłD15. SPI═©ą┼▌ö╚ļČ©Ģr(sh©¬)┐“łD

ĪĪĪĪ╚ńČ©Ģr(sh©¬)┐“łD╦∙╩ŠŻ¼╦∙ėą16╬╗öĄ(sh©┤)ō■(j©┤)Š∙į┌├┐éĆ(g©©)Ģr(sh©¬)ńŖų▄Ų┌╔ŽĒś┤╬é„▀fŻ¼Č°Ų¼▀x┐žųŲŠĆŻ©chip select line)ät│╩¼F(xi©żn)Ą═ļŖŲĮĪŻ ¼F(xi©żn)į┌Ż¼╬ęéāüĒ┐┤┐┤į┌NI LabVIEW FPGAųąŻ¼╚ń║╬═©▀^ųŪ─▄DAQė▓╝■╔ŽĄ─3ŚlöĄ(sh©┤)ūųŠĆ▀M(j©¼n)ąą┤╦ŅÉŠÄ│╠ĪŻ

ėęÖ┌

ėęÖ┌

╝ė║├ėč

╝ė║├ėč  ░l(f©Ī)Č╠ą┼

░l(f©Ī)Č╠ą┼

Post ByŻ║2010-11-20 9:25:13

Post ByŻ║2010-11-20 9:25:13

╝ė║├ėč

╝ė║├ėč  ░l(f©Ī)Č╠ą┼

░l(f©Ī)Č╠ą┼

Post ByŻ║2010-12-4 21:36:53

Post ByŻ║2010-12-4 21:36:53